Synopsys Accelerates Chip Design with AI Copilot Release

This week, electronic design automation (EDA) leader Synopsys unveiled expansions to its Synopsys.ai Copilot generative AI capabilities, promising to transform workflows for semiconductor engineering teams, enabling them to take on more complex designs on accelerated timelines.

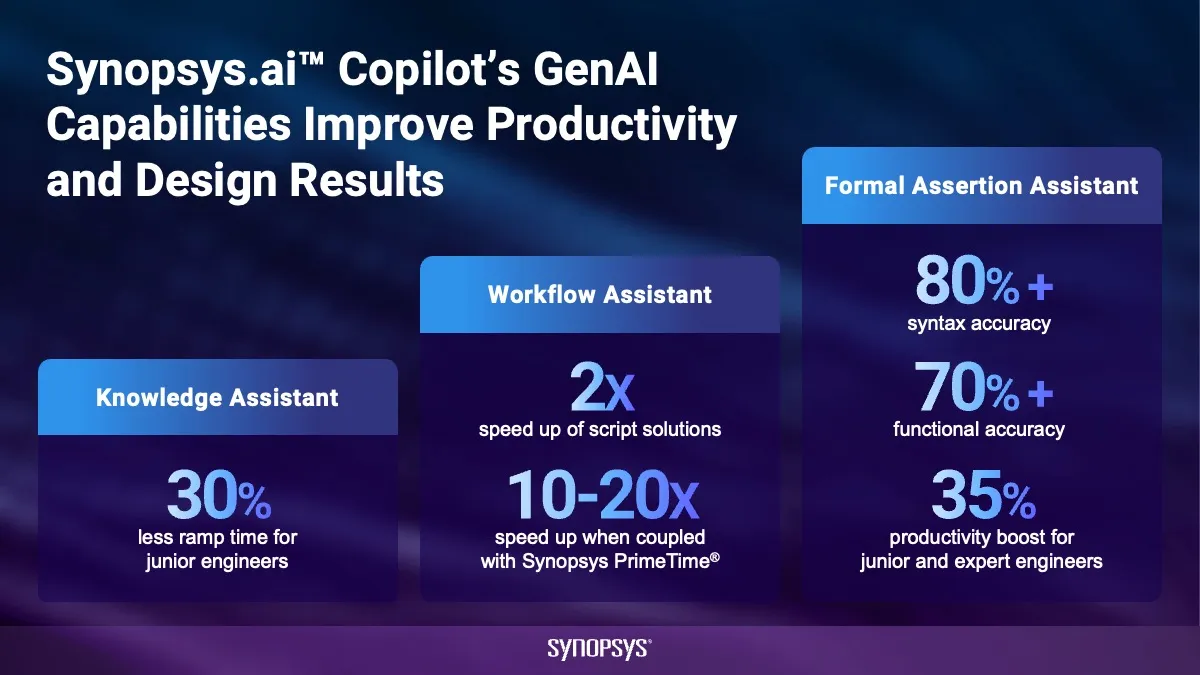

Synopsys reports that the new generative AI (Gen AI) capabilities accelerate workflows that previously consumed days into tasks completed in mere hours, and processes that took hours into operations finished in minutes. Early adopters are already reporting extraordinary gains: 30% faster ramp time for early-career engineers using knowledge assistant and 35% boost in engineering productivity for early-career and expert engineers within formal verification workflows using formal assertion assistant.

At the heart of this transformation lies Synopsys.ai Copilot’s dual approach: assistive and creative AI capabilities. The assistive features focus on knowledge management and workflow optimization, helping engineers to navigate complex documentation, generate scripts, and guide newcomers through the labyrinthine world of chip design. The creative capabilities venture into more ambitious territory, automatically generating formal assertions and register-transfer level (RTL) code with greater than 80% syntax accuracy and more than 70% functional accuracy.

This AI expansion gains additional significance when viewed through the lens of Synopsys’ recently completed acquisition of Ansys. The integration is already paying off with the recent introduction of Ansys Engineering Copilot and updates to Ansys SimAI, extending AI capabilities deep into simulation and analysis workflows.

In addition, Synopsys is looking beyond current generative AI applications toward what it calls AgentEngineer technology for chip design. Developed in collaboration with Microsoft, this represents a progression toward increasingly autonomous design systems. The company envisions a five-level evolution: from step-level actions (L2) to complex multi-agent operations (L3), dynamic flow optimization with adaptive learning (L4), and ultimately autonomous decision making (L5).

The first prototype offers a glimpse of a future where AI agents don’t just assist engineers but actively participate in the design process. As Microsoft’s Aseem Datar notes, “Together, we are not just optimizing existing workflows—we are introducing a new paradigm to advance engineering innovation and productivity for next-generation chip designs.”

The TechArena Take

In an industry where time-to-market can determine billion-dollar market positions, Synopsys has just handed its customers a significant advantage. The timing is particularly crucial as the industry grapples with a combination of design complexity and workforce shortages. Advanced AI chips require sophisticated design methodologies, while simultaneously, the pool of experienced semiconductor engineers remains constrained.

Synopsys’ AI capabilities directly address this paradox by accelerating novice engineers’ learning curves while amplifying expert productivity. The real test will be execution at scale, but the early results suggest meaningful progress toward AI becoming a more integral part of the semiconductor design process.